Subthreshold and Near-Threshold Analog Techniques

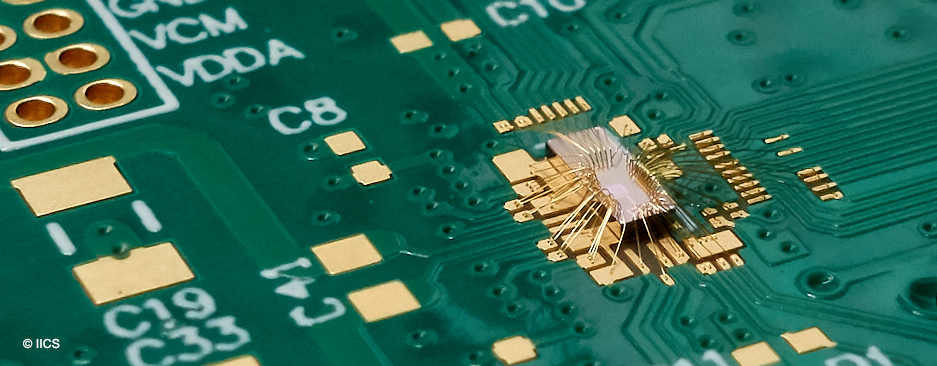

The design of analog integrated circuits under ultra-low supply voltages is driven by the continued technology scaling as well as the increased demand for energy efficiency. We are working on the analog design techniques under 0.1-0.5 V voltages, including body-input, inverter-based, replica-bias, leakage reduction, etc. circuit-level techniques and low-swing architectures. We have demonstrated the first analog design under 0.15V, an 8b SAR ADC, and a series of 0.2-0.4V delta-sigma modulators. We propose a systematical approach to implementing conventional amplifier structures with inverters, allowing ultra-low voltage operation with increased flexibility in adopting traditional and well-proven circuit techniques. Moreover, we have also demonstrated PVT robust designs under sub/near-threshold supply voltages. In this area, we are leading an NSFC key project which is considered a recognition.

- Lishan Lv, Xiong Zhou, Zhiliang Qiao, and Qiang Li, "Inverter-based subthreshold amplifier techniques and their application in 0.3V ΔƩ-modulators," IEEE Journal of Solid-State Circuits (JSSC), vol. 54, no. 5, pp. 1436-1445, May 2019.

- Zhaoming Ding, Xiong Zhou, and Qiang Li, "A 0.5–1.1V adaptive bypassing SAR ADC utilizing the oscillation-cycle information of a VCO-based comparator," IEEE Journal of Solid-State Circuits (JSSC), vol. 54, no. 4, pp. 968-977, Apr. 2019. (Invited, Special Issue on VLSI Circuits)

- Lishan Lv, Ankesh Jain, Xiong Zhou, Joachim Becker, Qiang Li, and Maurits Ortmanns, "A 0.4V Gm-C proportional-integrator-based continuous-time ΔƩ modulator with 50kHz BW and 74.4dB SNDR," IEEE Journal of Solid-State Circuits (JSSC), vol. 53, no. 11, pp. 3256-3267, Nov. 2018.

- Xiaofei Ma, Yan Lu, R. Martins, Qiang Li, “A 0.4V 430nA quiescent current NMOS digital LDO with NAND-based analog-assisted loop in 28nm CMOS,” International Solid-State Circuits Conference (ISSCC), San Francisco, CA, United States, Feb. 11-15, 2018.

- Zhiliang Qiao, X. Zhou, and Qiang Li, "A 250mV 77dB DR 10kHz BW SC ΔΣ modulator exploiting subthreshold OTAs," 40th European Solid-State Circuits Conference (ESSCIRC), Venice, Italy, Sept. 22-26, 2014.

- Xiong Zhou, and Qiang Li, "A 160mV 670nW 8-bit SAR ADC in 0.13μm CMOS," IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, United States, Sept. 9-12, 2012.

Data Converters

The world is analog - data conversion is an enabler for any digital processing to interface the real world. The speed, resolution, linearity, and power of data converters determine system performance fundamentally. Therefore, data converter design is a forever lasting topic. Our current focus is on power-efficient SAR based ADCs, where the architecture is highly digital and the benefit of advanced CMOS technologies can be generally brought into ADC designs. Besides the ultra-low voltage ADCs designed under sub/near-threshold supplies, we are among the earliest that proposed the passive residue transfer techniques for pipelined/two-step SAR ADCs. A DAC architecture generating binary-weighted references recursively is proposed and demonstrated to be power- and area-efficient. We are recently studying the time-domain ADCs since the speed and time-domain resolution are both scaling favorable. We are the first that introduced the concept of "number of oscillation cycles (NOC)" in closed-loop VCO-based comparators, which serves as an inherent parallel coarse quantization as well as a metastability indicator. The closed-form metastability analysis of VCO-based comparators is carried out with a low-cost and quantitative measure of metastability proposed. From our recent work, VCO-based SAR ADCs with improved robustness and linearity are demonstrated due to the additional design space offered by the NOC.

- Zheng Zhu, Xiong Zhou, Yuheng Du, Yao Feng, and Qiang Li, "A 14-bit 4-MS/s VCO-based SAR ADC with deep metastability facilitated mismatch calibration," IEEE Journal of Solid-State Circuits (JSSC), vol. 55, no. 6, pp. 1565-1576, June 2020.

- Zhaoming Ding, Xiong Zhou, and Qiang Li, "A 0.5–1.1V adaptive bypassing SAR ADC utilizing the oscillation-cycle information of a VCO-based comparator," IEEE Journal of Solid-State Circuits (JSSC), vol. 54, no. 4, pp. 968-977, Apr. 2019. (Invited, Special Issue on VLSI Circuits)

- Lishan Lv, Ankesh Jain, Xiong Zhou, Joachim Becker, Qiang Li, and Maurits Ortmanns, "A 0.4V Gm-C proportional-integrator-based continuous-time ΔƩ modulator with 50kHz BW and 74.4dB SNDR," IEEE Journal of Solid-State Circuits (JSSC), vol. 53, no. 11, pp. 3256-3267, Nov. 2018.

- Haiwen Chen, Xiong Zhou, Qiang Yu, Fan Zhang and Qiang Li, "A >3GHz ERBW 1.1-GS/s 8-bit two-step SAR ADC with recursive-weight DAC," Symposium on VLSI Circuits, Honolulu, HI, United States, June 18-22, 2018.

- Zhaoming Ding, Xiong Zhou, and Qiang Li, "A 0.5-1.1V 10b adaptive bypassing SAR ADC utilizing oscillation cycle information of VCO-based comparator," Symposium on VLSI Circuits, Honolulu, HI, United States, June 18-22, 2018.

- Junfeng Gao, Guangjun Li, and Qiang Li, "An amplifier-free pipeline-SAR ADC architecture with enhanced speed and energy efficiency," IEEE Transactions on Circuits and Systems −II: Express Briefs (TCASII), vol. 63, no. 4, pp. 341-345, Apr. 2016.

Sensor/Biomedical/Noise Interfaces

We started working on the biopotential interface in the 2000s, demonstrating a rough but configurable front-end for ECG, EEG and EMG signals. Recently, we are working on biomedical interfaces for dry-contacted, flexible, and large-scale electrodes and arrays, where the impedance, CMRR, and offset are challenging considerations in addition to the standard issues, e.g., noise, power, etc. We proposed an active electrode architecture to accommodate the impedance challenge for dry-contacted electrodes, which has been demonstrated in an EEG acquisition system with dry-contacted flexible electrodes in the ear canal. We have also demonstrated high-CMRR techniques with general applications for instrumentation amplifiers. Moreover, to monitor the power supply noise on-chip, a subsampling and averaging based noise analyzer with compressed sensing has been proposed, enabling the practical on-chip PSN measurement with significantly improved performance and measurement speed.

- Pengfei Zhai, Zheng Zhu, Xiong Zhou, Yan Cai, Fan Zhang, and Qiang Li, "An on-chip power-supply noise analyzer with compressed sensing and enhanced quantization," IEEE Journal of Solid-State Circuits (JSSC), vol. 57, no. 1, pp. 302-311, Jan. 2022.

- Sanfeng Zhang, Xiong Zhou, Chen Gao, and Qiang Li, “A 130-dB CMRR instrumentation amplifier with common-mode replication,” IEEE Journal of Solid-State Circuits (JSSC), vol. 57, no. 1, pp. 278-289, Jan. 2022.

- Sanfeng Zhang, Xiong Zhou, Chen Gao, and Qiang Li, “An AC-coupled instrumentation amplifier achieving 110dB CMRR at 50Hz with chopped pseudoresistors and successive-approximation-based capacitor trimming,” IEEE Journal of Solid-State Circuits (JSSC), vol. 56, no. 1, pp. 277-286, Jan. 2021.

- Sanfeng Zhang, Chen Gao, Xiong Zhou, and Qiang Li, “A 130dB-CMRR instrumentation amplifier with common-mode replication,” International Solid-State Circuits Conference (ISSCC), San Francisco, CA, United States, Feb. 16-20, 2020.

- Pengfei Zhai, Xiong Zhou, Yan Cai, Zheng Zhu, Fan Zhang, and Qiang Li, “A scalable 20GHz on-die power supply noise analyzer with compressed sensing,” International Solid-State Circuits Conference (ISSCC), San Francisco, CA, United States, Feb. 16-20, 2020.

- Xiong Zhou, Qiang Li, S. Kilsgaard, F. Moradi, S. Kappel, and P. Kidmose, "A wearable ear-EEG recording system based on dry-contact active electrodes," Symposium on VLSI Circuits, Honolulu, HI, United States, June 13-17, 2016, pp. 260-261.

- Qiang Li, Roy Tan, and Rajinder Singh, "A 1-V 36-µW low-noise adaptive interface IC for portable biomedical applications," 33rd European Solid-State Circuits Conference (ESSCIRC), Munich, Germany, Sept. 11-13, 2007, pp. 288-291.

RF Integrated Circuits

We studied the linearity limitation of RF switches in bulk CMOS in the 2000s, where we revealed the mechanism of unintentional turn-on of the reverse-biased parasitic diodes. Double-well body-floating technique was therefore proposed to enhance the linearity of CMOS RF switches, which has now become a widely adopted technique in CMOS RF IC designs. We were also among the first that customized transistor layout with increased drain-source distance to minimize the lateral coupling due to interconnections. Wideband resistive-feedback impedance matching with gain-enhanced noise-cancellation technique was proposed, and capacitive peaking traditionally adopted in transimpedance amplifier design was incorporated, leading to inductorless wideband LNAs. In recent years, we have demonstrated highly-linear phase shifters, power amplifiers, and phased-array transceivers for X- and Ka-band applications.

- Chao Liu, Qiang Li, Y. Li, X. Deng, H. Tang, R. Wang, H. Liu, Yongzhong Xiong, "A Ka-band single-chip SiGe BiCMOS phased-array transmit/receive front-end," IEEE Transactions on Microwave Theory and Techniques (TMTT), vol. 64, no. 11, pp. 3667-3677, Nov. 2016.

- Chao Liu, Qiang Li, Y. Li, X. Li, H. Liu, Yongzhong Xiong, "A fully integrated X-band phased array transceiver in 0.13-µm SiGe BiCMOS technology," IEEE Transactions on Microwave Theory and Techniques (TMTT), vol. 64, no. 2, pp. 575-584, Feb. 2016.

- Chao Liu, Qiang Li, Y. Li, X. Li, H. Liu, Y.-Z. Xiong, "An 890mW stacked power amplifier using SiGe HBTs for X-band multifunctional chips," 41st European Solid-State Circuits Conference (ESSCIRC), Graz, Austria, Sept. 14-18, 2015.

- Qiang Li, Y. P. Zhang, Kiat-Seng Yeo, and W. M. Lim, "16.6- and 28-GHz fully integrated CMOS RF switches with improved body-floating," IEEE Transactions on Microwave Theory and Techniques (TMTT), vol. 56, no. 2, pp. 339-345, Feb. 2008.

- Qiang Li, and Y. P. Zhang, "A 1.5-V 2−9.6-GHz inductorless low-noise amplifier in 0.13-μm CMOS," IEEE Transactions on Microwave Theory and Techniques (TMTT), vol. 55, no. 10, pp. 2015-2023, Oct. 2007. (No. 1 of the top 10 papers accessed in MTT, October 2007.)

- Qiang Li, and Y. P. Zhang, "CMOS T/R switch design: towards ultra-wideband and higher frequency," IEEE Journal of Solid-State Circuits (JSSC), vol. 42, no. 3, pp. 563-570, Mar. 2007. (No. 36 of the top 100 documents accessed in IEEEXplore, March 2007.)

Preliminary, Collaborative and Miscellaneous Studies

We are actively looking at emerging areas as well as working with researchers, engineers, and entrepreneurs in a broader domain. Recently, we are collaborating with Prof. Meng-Fan Chang from National Tsing Hua University in the area of in-memory computing, a non-Von-Neumann computer architecture. We are also working with medical doctors, device engineers, material scientists and chemists for interesting ideas where electronics are indispensable.

- Q. Huo, Y. Yang, Y. Wang, D. Lei, X. Fu, Q. Ren, X. Xu, Q. Luo, G. Xing, X. Chen, Xin Si, H. Wu, Y. Yuan, Qiang Li, X. Li, X. Wang, Meng-Fan Chang, Feng Zhang, and Ming Liu, “A computing-in-memory macro based on three-dimensional resistive random-access memory,” Nature Electronics, vol. 5, pp. 469-477, July 2022.

- Xin Si, Y.-N. Tu, W.-H. Huang, J.-W. Su, P.-J. Lu, J.-H. Wang, T.-W. Liu, S.-Y. Wu, R. Liu, Y.-C. Chou, Z. Zhang, S.-H. Sie, W.-C. Wei, Y.-C. Lo, T.-H. Wen, T.-H. Hsu, Y.-K. Chen, W. Shih, C.-C. Lo, R.-S. Liu, C.-C. Hsieh, K.-T. Tang, N.-C. Lien, W.-C. Shih, Y. He, Qiang Li, and Meng-Fan Chang, “A 28nm 64Kb 6T SRAM computing-in-memory macro with 8b MAC operation for AI edge chips,” International Solid-State Circuits Conference (ISSCC), San Francisco, CA, United States, Feb. 16-20, 2020.

- Xin Si, J.-J. Chen, Y.-N. Tu, W.-H. Huang, J.-H. Wang, Y.-C. Chiu, W.-C. Wei, S.-Y. Wu, X. Sun, R. Liu, S. Yu, R.-S. Liu, C.-C. Hsieh, K.-T. Tang, Qiang Li, and Meng-Fan Chang, “A twin-8T SRAM computation-in-memory unit-macro for multiple-bit CNN based AI edge processors,” IEEE Journal of Solid-State Circuits (JSSC), vol. 55, no. 1, Jan. 2020.

- Ying Zhao, Ling Li, Y. Peng, Q. Li, G. Yang, X. Chuai, Qiang Li, G. Han, and Ming Liu, "Surface potential-based compact model for negative capacitance FETs compatible for logic circuit: with time dependence and multidomain interaction," IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, United States, Dec. 7-11, 2019.

- Xin Si, Jia-Jing Chen, Y.-N. Tu, W.-H. Huang, J.-H. Wang, W.-C. Wei, S.-Y. Wu, X. Sun, R. Liu, S. Yu, R.-S. Liu, C.-C. Hsieh, K.-T. Tang, Qiang Li, Meng-Fan Chang, “A twin-8T SRAM computation-in-memory macro for multiple-bit CNN based machine learning,” International Solid-State Circuits Conference (ISSCC), San Francisco, CA, United States, Feb. 17-21, 2019.

- Win-San Khwa, Jia-Jing Chen, Jia-Fang Li, Xin Si, En-Yu Yang, Xiaoyu Sun, Rui Liu, Pai-Yu Chen, Qiang Li, Shimeng Yu, Meng-Fan Chang, “A 65nm 4Kb algorithm-dependent computing-in-memory SRAM unit-macro with 2.3ns and 55.8TOPS/W fully parallel product-sum operation for binary DNN edge processors,” International Solid-State Circuits Conference (ISSCC), San Francisco, CA, United States, Feb. 11-15, 2018.

- C. Chen, M. Xue, Y. Wen, G. Yao, Y. Cui, F. Liao, Z. Yan, L. Huang, S. A. Khan, Min Gao, T. Pan, H. Zhang, W. Jing, D. Guo, Sanfeng Zhang, Hailiang Yao, Xiong Zhou, Qiang Li, Yang Xia, and Yuan Lin, “A Ferroelectric Ceramic/Polymer Composite-Based Capacitive Electrode Array for In Vivo Recordings,” Advanced Healthcare Materials, vol. 6, no. 16, pp. 3667-3677, Aug. 2017.